## Features

- High-performance, Low-power AVR<sup>®</sup> 8-bit Microcontroller

- Advanced RISC Architecture

- 130 Powerful Instructions Most Single Clock Cycle Execution

- 32 x 8 General Purpose Working Registers + Peripheral Control Registers

- Fully Static Operation

- Up to 16 MIPS Throughput at 16 MHz

- On-chip 2-cycle Multiplier

- High Endurance Non-volatile Memory segments

- 64K Bytes of In-System Reprogrammable Flash program memory

- 2K Bytes EEPROM

- 4K Bytes Internal SRAM

- Write/Erase Cycles: 10,000 Flash/100,000 EEPROM

- Data retention: 20 years at 85°C/100 years at 25°C<sup>(1)</sup>

- Optional Boot Code Section with Independent Lock Bits In-System Programming by On-chip Boot Program True Read-While-Write Operation

- Up to 64K Bytes Optional External Memory Space

- Programming Lock for Software Security

- SPI Interface for In-System Programming

- JTAG (IEEE std. 1149.1 Compliant) Interface

- Boundary-scan Capabilities According to the JTAG Standard

- Extensive On-chip Debug Support

- Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

- Peripheral Features

- Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes

- Two Expanded 16-bit Timer/Counters with Separate Prescaler, Compare Mode, and Capture Mode

- Real Time Counter with Separate Oscillator

- Two 8-bit PWM Channels

- 6 PWM Channels with Programmable Resolution from 1 to 16 Bits

- 8-channel, 10-bit ADC

- 8 Single-ended Channels

- 7 Differential Channels

- 2 Differential Channels with Programmable Gain (1x, 10x, 200x)

- Byte-oriented Two-wire Serial Interface

- Dual Programmable Serial USARTs

- Master/Slave SPI Serial Interface

- Programmable Watchdog Timer with On-chip Oscillator

- On-chip Analog Comparator

- Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal Calibrated RC Oscillator

- External and Internal Interrupt Sources

- Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby and Extended Standby

- Software Selectable Clock Frequency

- ATmega103 Compatibility Mode Selected by a Fuse

- Global Pull-up Disable

- I/O and Packages

- 53 Programmable I/O Lines

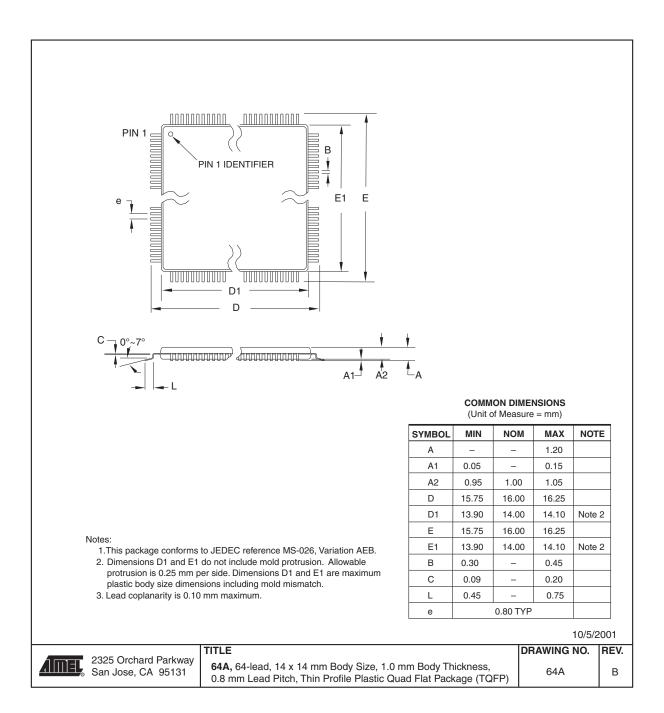

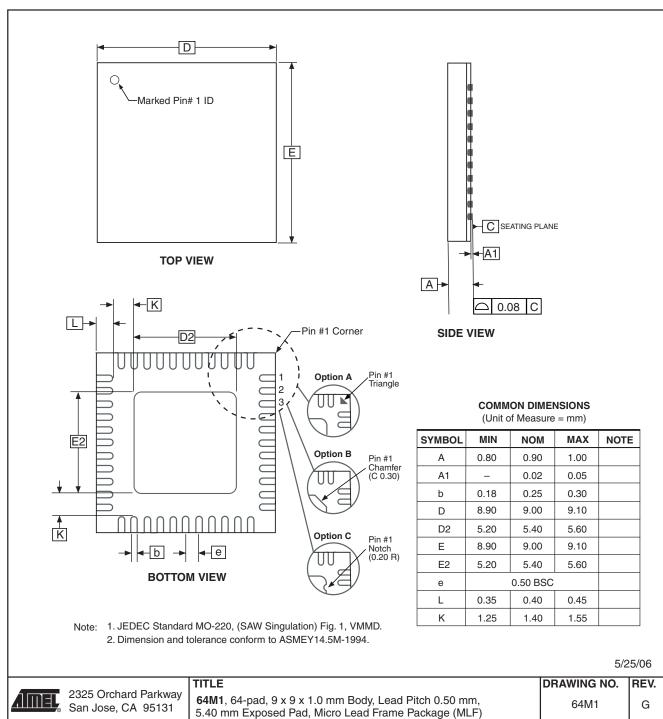

- 64-lead TQFP and 64-pad QFN/MLF

- Operating Voltages

- 2.7 5.5V for ATmega64L

- 4.5 5.5V for ATmega64

- Speed Grades

- 0 8 MHz for ATmega64L

- 0 16 MHz for ATmega64

8-bit **AVR**<sup>®</sup> Microcontroller with 64K Bytes In-System Programmable Flash

ATmega64 ATmega64L

## Summary

2490PS-AVR-07/09

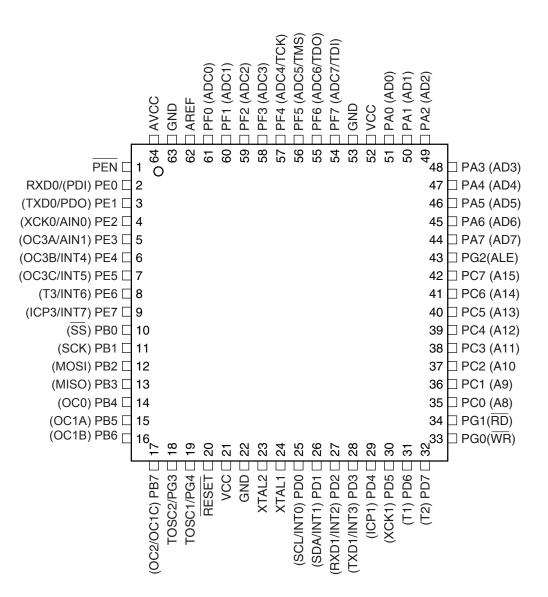

Figure 1. Pinout ATmega64

## Pin Configuration

TQFP/MLF

### Disclaimer

Typical values contained in this data sheet are based on simulations and characterization of other AVR microcontrollers manufactured on the same process technology. Min and Max values will be available after the device is characterized.

# <sup>2</sup> ATmega64(L)

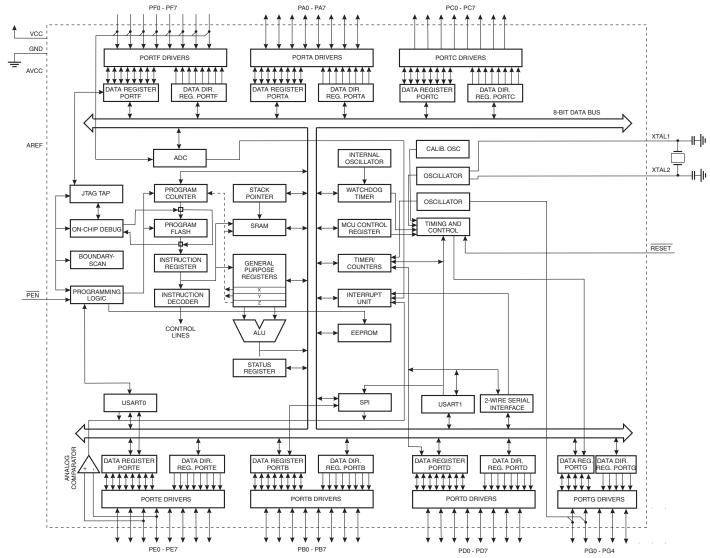

### **Overview**

The ATmega64 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega64 achieves throughputs approaching 1 MIPS per MHz, allowing the system designer to optimize power consumption versus processing speed.

### **Block Diagram**

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega64 provides the following features: 64K bytes of In-System Programmable Flash with Read-While-Write capabilities, 2K bytes EEPROM, 4K bytes SRAM, 53 general purpose I/O lines, 32 general purpose working registers, Real Time Counter (RTC), four flexible Timer/Counters with compare modes and PWM, two USARTs, a byte oriented Two-wire Serial Interface, an 8-channel, 10-bit ADC with optional differential input stage with programmable gain, programmable Watchdog Timer with internal Oscillator, an SPI serial port, IEEE std. 1149.1 compliant JTAG test interface, also used for accessing the On-chip Debug system and programming, and six software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or Hardware Reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except asynchronous timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low power consumption. In Extended Standby mode, both the main Oscillator and the asynchronous timer continue to run.

The device is manufactured using Atmel's high-density non-volatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed In-System through an SPI serial interface, by a conventional non-volatile memory programmer, or by an On-chip Boot program running on the AVR core. The Boot Program can use any interface to download the Application Program in the Application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega64 is a powerful microcontroller that provides a highly-flexible and cost-effective solution to many embedded control applications.

The ATmega64 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, In-Circuit Emulators, and evaluation kits.

### ATmega103 and ATmega64 Compatibility

The ATmega64 is a highly complex microcontroller where the number of I/O locations supersedes the 64 I/O location reserved in the AVR instruction set. To ensure backward compatibility with the ATmega103, all I/O locations present in ATmega103 have the same location in ATmega64. Most additional I/O locations are added in an Extended I/O space starting from 0x60 to 0xFF (i.e., in the ATmega103 internal RAM space). These location can be reached by using LD/LDS/LDD and ST/STS/STD instructions only, not by using IN and OUT instructions. The relocation of the internal RAM space may still be a problem for ATmega103 users. Also, the increased number of Interrupt Vectors might be a problem if the code uses absolute addresses. To solve these problems, an ATmega103 compatibility mode can be selected by programming the fuse M103C. In this mode, none of the functions in the Extended I/O space are in use, so the internal RAM is located as in ATmega103. Also, the extended Interrupt Vectors are removed.

The ATmega64 is 100% pin compatible with ATmega103, and can replace the ATmega103 on current printed circuit boards. The application notes "Replacing ATmega103 by ATmega128" and "Migration between ATmega64 and ATmega128" describes what the user should be aware of replacing the ATmega103 by an ATmega128 or ATmega64.

### ATmega103 Compatibility Mode

By programming the M103C Fuse, the ATmega64 will be compatible with the ATmega103 regards to RAM, I/O pins and Interrupt Vectors as described above. However, some new features in ATmega64 are not available in this compatibility mode, these features are listed below:

- One USART instead of two, asynchronous mode only. Only the eight least significant bits of the Baud Rate Register is available.

- One 16 bits Timer/Counter with two compare registers instead of two 16 bits Timer/Counters with three compare registers.

- Two-wire serial interface is not supported.

- Port G serves alternate functions only (not a general I/O port).

- Port F serves as digital input only in addition to analog input to the ADC.

- Boot Loader capabilities is not supported.

- It is not possible to adjust the frequency of the internal calibrated RC Oscillator.

- The External Memory Interface can not release any Address pins for general I/O, neither configure different wait states to different External Memory Address sections.

- Only EXTRF and PORF exist in the MCUCSR Register.

- No timed sequence is required for Watchdog Timeout change.

- Only low-level external interrupts can be used on four of the eight External Interrupt sources.

- Port C is output only.

- USART has no FIFO buffer, so Data OverRun comes earlier.

- The user must have set unused I/O bits to 0 in ATmega103 programs.

### **Pin Descriptions**

| VCC | Digital supply voltage. |

|-----|-------------------------|

|     |                         |

GND Ground.

**Port A (PA7..PA0)** Port A is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port A also serves the functions of various special features of the ATmega64 as listed on page 73.

**Port B (PB7..PB0)** Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B also serves the functions of various special features of the ATmega64 as listed on page 74.

| Port C (PC7PC0) | Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                                           |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Port C also serves the functions of special features of the ATmega64 as listed on page 77. In ATmega103 compatibility mode, Port C is output only, and the port C pins are <b>not</b> tri-stated when a reset condition becomes active.                                                                                                                                                                                                                                                                                                                                                                                                             |

| Port D (PD7PD0) | Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                                           |

|                 | Port D also serves the functions of various special features of the ATmega64 as listed on page 78.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Port E (PE7PE0) | Port E is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port E output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port E pins that are externally pulled low will source current if the pull-up resistors are activated. The Port E pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                                           |

|                 | Port E also serves the functions of various special features of the ATmega64 as listed on page 81.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Port F (PF7PF0) | Port F serves as the analog inputs to the A/D Converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                 | Port F also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used. Port pins can provide internal pull-up resistors (selected for each bit). The Port F output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port F pins that are externally pulled low will source current if the pull-up resistors are activated. The Port F pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PF7(TDI), PF5(TMS) and PF4(TCK) will be activated even if a reset occurs. |

|                 | The TDO pin is tri-stated unless TAP states that shift out data are entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 | Port F also serves the functions of the JTAG interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 | In ATmega103 compatibility mode, Port F is an input port only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Port G (PG4PG0) | Port G is a 5-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port G output buffers have symmetrical drive characteristics with both high sink and source                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 | capability. As inputs, Port G pins that are externally pulled low will source current if the pull-up resistors are activated. The Port G pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                                                                                                                                                                                                                                               |

|                 | resistors are activated. The Port G pins are tri-stated when a reset condition becomes active,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 | resistors are activated. The Port G pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RESET | Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table 19 on page                                    |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 52. Shorter pulses are not guaranteed to generate a reset.                                                                                                                                                                      |

| XTAL1 | Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.                                                                                                                                  |

| XTAL2 | Output from the inverting Oscillator amplifier.                                                                                                                                                                                 |

| AVCC  | AVCC is the supply voltage pin for Port F and the A/D Converter. It should be externally connected to $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to $V_{CC}$ through a low-pass filter. |

| AREF  | AREF is the analog reference pin for the A/D Converter.                                                                                                                                                                         |

| PEN   | This is a programming enable pin for the SPI Serial Programming mode. By holding this pin low during a Power-on Reset, the device will enter the SPI Serial Programming mode. PEN has no                                        |

function during normal operation.

**Resources** A comprehensive set of development tools, application notes and datasheetsare available for download on http://www.atmel.com/avr.

**Data Retention** Reliability Qualification results show that the projected data retention failure rate is much less than 1 PPM over 20 years at 85°C or 100 years at 25°C.

## **Register Summary**

| Address                    | Name                 | Bit 7       | Bit 6       | Bit 5       | Bit 4                                  | Bit 3             | Bit 2        | Bit 1                   | Bit 0      | Page       |

|----------------------------|----------------------|-------------|-------------|-------------|----------------------------------------|-------------------|--------------|-------------------------|------------|------------|

|                            |                      |             |             |             |                                        |                   |              |                         |            | Faye       |

| (0xFF)                     | Reserved             | -           | -           | -           | -                                      | -                 | -            | -                       | -          |            |

|                            | Reserved             | -           | -           | -           | -                                      | -                 | -            | -                       | -          |            |

| (0x9E)                     | Reserved             | -           | -           | -           | -                                      | -                 | -            | -                       | -          | 101        |

| (0x9D)                     | UCSR1C               | -           | UMSEL1      | UPM11       | UPM10                                  | USBS1             | UCSZ11       | UCSZ10                  | UCPOL1     | 191        |

| (0x9C)                     | UDR1                 | EVO1        | TYON        |             |                                        | Data Register     |              | 1101/1                  | 100014     | 188        |

| (0x9B)                     | UCSR1A               | RXC1        | TXC1        | UDRE1       | FE1                                    | DOR1              | UPE1         | U2X1                    | MPCM1      | 189        |

| (0x9A)                     | UCSR1B               | RXCIE1      | TXCIE1      | UDRIE1      | RXEN1                                  | TXEN1             | UCSZ12       | RXB81                   | TXB81      | 190        |

| (0x99)                     | UBRR1L               |             |             |             | USARTIBAUG                             | Rate Register Lo  |              | Dete De sister Hist     | -          | 193        |

| (0x98)<br>(0x97)           | UBRR1H               | -           | -           | -           | -                                      |                   |              | Rate Register High      |            | 193        |

| (0x97)<br>(0x96)           | Reserved             | _           |             |             |                                        | -                 |              | -                       | -          |            |

| , ,                        | Reserved             | _           |             |             |                                        | -                 |              |                         | UCPOL0     | 101        |

| (0x95)<br>(0x94)           | UCSR0C               |             | UMSEL0      | UPM01       | UPM00                                  | USBS0             | UCSZ01       | UCSZ00                  |            | 191        |

| (0x94)<br>(0x93)           | Reserved<br>Reserved | -           | -           | -           | -                                      | -                 | -            | -                       | -          |            |

| (0x93)<br>(0x92)           |                      |             | 1           |             | -                                      | -                 | _            | _                       | -          |            |

| (0x92)<br>(0x91)           | Reserved<br>Reserved | -           | -           | -           | -                                      | -                 | -            | -                       | -          |            |

| (0x91)<br>(0x90)           | UBRR0H               | _           | -           | _           | -                                      | -                 |              | –<br>Poto Rogistor High |            | 193        |

| (0x90)<br>(0x8F)           |                      | _           |             |             |                                        |                   | USARTU Bauur | Rate Register High      |            | 195        |

| (0x8F)<br>(0x8E)           | Reserved<br>ADCSRB   | -           | -           | -           | -                                      | -                 | ADTS2        | –<br>ADTS1              | -<br>ADTS0 | 247        |

| (0x8E)<br>(0x8D)           | Reserved             | -           | -           | -           | -                                      | -                 | AD152        | AD151                   | ADTS0      | 241        |

| (0x8D)<br>(0x8C)           | TCCR3C               | –<br>FOC3A  | FOC3B       | FOC3C       | _                                      | _                 | _            |                         | _          | 138        |

| (0x8C)<br>(0x8B)           | TCCR3C<br>TCCR3A     | COM3A1      | COM3A0      | COM3B1      | –<br>COM3B0                            | –<br>COM3C1       | –<br>COM3C0  | –<br>WGM31              | -<br>WGM30 | 138        |

| (0x8B)<br>(0x8A)           | TCCR3A<br>TCCR3B     | ICNC3       | ICES3       | - COM3B1    | WGM33                                  | WGM32             | CS32         | CS31                    | CS30       | 132        |

| (0x8A)<br>(0x89)           | TCOR3B<br>TCNT3H     | ICINC3      | ICE33       |             | er/Counter3 – Co                       |                   |              | 0331                    | 0330       | 138        |

| (0x89)<br>(0x88)           | TCNT3H<br>TCNT3L     |             |             |             | er/Counter3 – Co                       |                   |              |                         |            | 138        |

| (0x88)<br>(0x87)           | OCR3AH               |             |             |             | unter3 – Output C                      | *                 |              |                         |            | 138        |

|                            |                      |             |             |             |                                        | 1 0               | 0,           |                         |            |            |

| (0x86)<br>(0x85)           | OCR3AL<br>OCR3BH     |             |             |             | unter3 – Output C<br>unter3 – Output C |                   |              |                         |            | 139<br>139 |

| (0x85)<br>(0x84)           | OCR3BH               |             |             |             | unter3 – Output C<br>unter3 – Output C |                   |              |                         |            | 139        |

|                            |                      |             |             |             |                                        | · ·               |              |                         |            |            |

| (0x83)<br>(0x82)           | OCR3CH<br>OCR3CL     |             |             |             | unter3 – Output C<br>unter3 – Output C |                   | * /          |                         |            | 139<br>139 |

| (0x82)<br>(0x81)           | ICR3H                |             |             |             | Counter3 – Input (                     |                   |              |                         |            | 139        |

| (0x80)                     | ICR3H                |             |             |             |                                        |                   |              |                         |            | 140        |

| (0x80)<br>(0x7F)           | Reserved             | _           | -           | -           | Counter3 – Input                       |                   | Low Byte     | -                       | -          | 140        |

| (0x7E)                     | Reserved             | _           | _           | _           | _                                      | _                 | _            | _                       | _          |            |

| (0x7D)                     | ETIMSK               | _           |             | TICIE3      | OCIE3A                                 | OCIE3B            | TOIE3        | OCIE3C                  | OCIE1C     | 141        |

| (0x7C)                     | ETIFR                | _           | _           | ICF3        | OCF3A                                  | OCF3B             | TOV3         | OCF3C                   | OCF1C      | 141        |

| (0x7B)                     | Reserved             | _           | _           | -           | -                                      | -                 | -            | -                       | -          | 172        |

| (0x7A)                     | TCCR1C               | FOC1A       | FOC1B       | FOC1C       | _                                      | _                 | _            | _                       | _          | 137        |

| (0x79)                     | OCR1CH               | TOOTA       | 10018       |             | unter1 – Output C                      |                   |              | _                       |            | 139        |

| (0x78)                     | OCR1CL               |             |             |             | unter1 – Output C                      | i e               | ů j          |                         |            | 139        |

| (0x77)                     | Reserved             | _           | _           | -           | _                                      | _                 | -            | _                       | _          | 100        |

| (0x76)                     | Reserved             | _           | _           | _           | _                                      | _                 | _            | _                       | _          |            |

| (0x75)                     | Reserved             | _           | _           | _           | _                                      | _                 | _            | _                       | _          |            |

| (0x73)<br>(0x74)           | TWCR                 | TWINT       | TWEA        | TWSTA       | TWSTO                                  | TWWC              | TWEN         | _                       | TWIE       | 206        |

| (0x74)<br>(0x73)           | TWDR                 |             |             |             | Two-wire Serial In                     |                   |              |                         |            | 208        |

| (0x73)<br>(0x72)           | TWDR                 | TWA6        | TWA5        | TWA4        | TWA3                                   | TWA2              | TWA1         | TWA0                    | TWGCE      | 208        |

| (0x72)<br>(0x71)           | TWAR                 | TWA0        | TWA5        | TWS5        | TWA3                                   | TWA2<br>TWS3      | -            | TWPS1                   | TWPS0      | 208        |

| (0x71)<br>(0x70)           | TWBR                 | 1007        | 11100       |             | /o-wire Serial Inte                    |                   | aister       | 1                       | 1111 00    | 207        |

| (0x70)<br>(0x6F)           | OSCCAL               | 1           |             | 1 1         |                                        | ibration Register | 9.0101       |                         |            | 43         |

| (0x6E)                     | Reserved             | _           | -           | _           | -                                      | –                 | -            | -                       | -          | UF.        |

| (0x6D)                     | XMCRA                | _           | SRL2        | SRL1        | <br>SRL0                               | SRW01             | SRW00        | SRW11                   |            | 32         |

| (0x6C)                     | XMCRB                | <br>XMBK    | -           | -           | -                                      | -                 | XMM2         | XMM1                    | XMM0       | 34         |

| (0x6B)                     | Reserved             | -           | _           | _           | _                                      | _                 | -            | -                       | -          |            |

| (0x6A)                     | EICRA                | ISC31       | ISC30       | ISC21       | ISC20                                  | ISC11             | ISC10        | ISC01                   | ISC00      | 90         |

| (0x69)                     | Reserved             | -           | -           | -           | -                                      | -                 | -            | -                       | -          |            |

| (0x68)                     | SPMCSR               | SPMIE       | RWWSB       | _           | RWWSRE                                 | BLBSET            | PGWRT        | PGERS                   | SPMEN      | 281        |

| (0x67)                     | Reserved             | -           | -           | _           | -                                      | -                 | -            | -                       | -          | 201        |

| (0x66)                     | Reserved             | _           | _           | _           | _                                      | _                 | _            | _                       | _          |            |

| (0x65)                     | PORTG                | _           | _           | _           | PORTG4                                 | PORTG3            | PORTG2       | PORTG1                  | PORTG0     | 89         |

|                            | DDRG                 | -           | -           | -           | DDG4                                   | DDG3              | DDG2         | DDG1                    | DDG0       | 89         |

| (0x64)                     | DDING                |             |             |             | PING4                                  | PING3             | PING2        | PING1                   | PING0      | 89         |

| (0x64)<br>(0x63)           | PING                 | _           |             |             |                                        |                   |              |                         |            |            |

| (0x64)<br>(0x63)<br>(0x62) | PING<br>PORTF        | –<br>PORTF7 | –<br>PORTF6 | –<br>PORTF5 | PING4<br>PORTF4                        | PORTF3            | PORTF2       | PORTF1                  | PORTF0     | 88         |

### ATmega64(L) 10

| Address     | Name          | Bit 7          | Bit 6  | Bit 5    | Bit 4             | Bit 3              | Bit 2       | Bit 1             | Bit 0        | Page              |

|-------------|---------------|----------------|--------|----------|-------------------|--------------------|-------------|-------------------|--------------|-------------------|

| (0x60)      | Reserved      | -              | -      | -        | -                 | -                  | -           | -                 | -            |                   |

| 0x3F (0x5F) | SREG          | I              | Т      | Н        | S                 | V                  | N           | Z                 | С            | 12                |

| 0x3E (0x5E) | SPH           | SP15           | SP14   | SP13     | SP12              | SP11               | SP10        | SP9               | SP8          | 14                |

| 0x3D (0x5D) | SPL           | SP7            | SP6    | SP5      | SP4               | SP3                | SP2         | SP1               | SP0          | 14                |

| 0x3C (0x5C) | XDIV          | XDIVEN         | XDIV6  | XDIV5    | XDIV4             | XDIV3              | XDIV2       | XDIV1             | XDIV0        | 39                |

| 0x3B (0x5B) | Reserved      | -              | -      | -        | -                 | -                  | -           | -                 | -            |                   |

| 0x3A (0x5A) | EICRB         | ISC71          | ISC70  | ISC61    | ISC60             | ISC51              | ISC50       | ISC41             | ISC40        | 91                |

| 0x39 (0x59) | EIMSK         | INT7           | INT6   | INT5     | INT4              | INT3               | INT2        | INT1              | INT0         | 92                |

| 0x38 (0x58) | EIFR          | INTF7          | INTF6  | INTF5    | INTF4             | INTF3              | INTF        | INTF1             | INTF0        | 92                |

| 0x37 (0x57) | TIMSK         | OCIE2          | TOIE2  | TICIE1   | OCIE1A            | OCIE1B             | TOIE1       | OCIE0             | TOIE0        | 109, 140, 160     |

| 0x36 (0x56) | TIFR          | OCF2           | TOV2   | ICF1     | OCF1A             | OCF1B              | TOV1        | OCF0              | TOV0         | 109, 142, 160     |

| 0x35 (0x55) | MCUCR         | SRE            | SRW10  | SE       | SM1               | SM0                | SM2         | IVSEL             | IVCE         | 32, 46, 64        |

| 0x34 (0x54) | MCUCSR        | JTD            | -      | -        | JTRF              | WDRF               | BORF        | EXTRF             | PORF         | 55, 256           |

| 0x33 (0x53) | TCCR0         | FOC0           | WGM00  | COM01    | COM00             | WGM01              | CS02        | CS01              | CS00         | 104               |

| 0x32 (0x52) | TCNT0         |                |        |          | Timer/Co          | unter0 (8 Bit)     |             |                   |              | 106               |

| 0x31 (0x51) | OCR0          |                | -      | Ti       | mer/Counter0 Ou   | tput Compare Re    | gister      |                   |              | 106               |

| 0x30 (0x50) | ASSR          | -              | -      | -        | -                 | AS0                | TCN0UB      | OCR0UB            | TCR0UB       | 107               |

| 0x2F (0x4F) | TCCR1A        | COM1A1         | COM1A0 | COM1B1   | COM1B0            | COM1C1             | COM1C0      | WGM11             | WGM10        | 132               |

| 0x2E (0x4E) | TCCR1B        | ICNC1          | ICES1  | -        | WGM13             | WGM12              | CS12        | CS11              | CS10         | 136               |

| 0x2D (0x4D) | TCNT1H        |                |        | Time     | er/Counter1 - Co  | unter Register Hig | gh Byte     |                   |              | 138               |

| 0x2C (0x4C) | TCNT1L        |                |        | Tim      | er/Counter1 – Co  | unter Register Lo  | w Byte      |                   |              | 138               |

| 0x2B (0x4B) | OCR1AH        |                |        | Timer/Co | unter1 – Output C | ompare Register    | A High Byte |                   |              | 139               |

| 0x2A (0x4A) | OCR1AL        |                |        | Timer/Co | unter1 – Output C | Compare Register   | A Low Byte  |                   |              | 139               |

| 0x29 (0x49) | OCR1BH        |                |        | Timer/Co | unter1 – Output C | ompare Register    | B High Byte |                   |              | 139               |

| 0x28 (0x48) | OCR1BL        |                |        | Timer/Co | unter1 – Output C | Compare Register   | B Low Byte  |                   |              | 139               |

| 0x27 (0x47) | ICR1H         |                |        | Timer/0  | Counter1 – Input  | Capture Register   | High Byte   |                   |              | 140               |

| 0x26 (0x46) | ICR1L         |                |        | Timer/   | Counter1 – Input  | Capture Register   | Low Byte    |                   |              | 140               |

| 0x25 (0x45) | TCCR2         | FOC2           | WGM20  | COM21    | COM20             | WGM21              | CS22        | CS21              | CS20         | 157               |

| 0x24 (0x44) | TCNT2         |                |        |          | Timer/Co          | unter2 (8 Bit)     |             |                   |              | 159               |

| 0x23 (0x43) | OCR2          |                |        | Tir      | mer/Counter2 Out  | put Compare Reg    | gister      |                   |              | 160               |

| 0x22 (0x42) | OCDR          | IDRD/<br>OCDR7 | OCDR6  | OCDR5    | OCDR4             | OCDR3              | OCDR2       | OCDR1             | OCDR0        | 253               |

| 0x21 (0x41) | WDTCR         | -              | -      | -        | WDCE              | WDE                | WDP2        | WDP1              | WDP0         | 57                |

| 0x20 (0x40) | SFIOR         | TSM            | -      | -        | -                 | ACME               | PUD         | PSR0              | PSR321       | 72, 111, 145, 227 |

| 0x1F (0x3F) | EEARH         | -              | -      | -        | -                 | -                  | EEPRON      | 1 Address Registe | er High Byte | 22                |

| 0x1E (0x3E) | EEARL         |                |        |          | EEPROM Addres     | s Register Low B   | yte         |                   |              | 22                |

| 0x1D (0x3D) | EEDR          |                |        |          | EEPROM            | Data Register      | 1           | 1                 |              | 22                |

| 0x1C (0x3C) | EECR          | -              | -      | -        | -                 | EERIE              | EEMWE       | EEWE              | EERE         | 22                |

| 0x1B (0x3B) | PORTA         | PORTA7         | PORTA6 | PORTA5   | PORTA4            | PORTA3             | PORTA2      | PORTA1            | PORTA0       | 87                |

| 0x1A (0x3A) | DDRA          | DDA7           | DDA6   | DDA5     | DDA4              | DDA3               | DDA2        | DDA1              | DDA0         | 87                |

| 0x19 (0x39) | PINA          | PINA7          | PINA6  | PINA5    | PINA4             | PINA3              | PINA2       | PINA1             | PINA0        | 87                |

| 0x18 (0x38) | PORTB         | PORTB7         | PORTB6 | PORTB5   | PORTB4            | PORTB3             | PORTB2      | PORTB1            | PORTB0       | 87                |

| 0x17 (0x37) | DDRB          | DDB7           | DDB6   | DDB5     | DDB4              | DDB3               | DDB2        | DDB1              | DDB0         | 87                |

| 0x16 (0x36) | PINB          | PINB7          | PINB6  | PINB5    | PINB4             | PINB3              | PINB2       | PINB1             | PINB0        | 87                |

| 0x15 (0x35) | PORTC         | PORTC7         | PORTC6 | PORTC5   | PORTC4            | PORTC3             | PORTC2      | PORTC1            | PORTC0       | 87                |

| 0x14 (0x34) | DDRC          | DDC7           | DDC6   | DDC5     | DDC4              | DDC3               | DDC2        | DDC1              | DDC0         | 87                |

| 0x13 (0x33) | PINC          | PINC7          | PINC6  | PINC5    | PINC4             | PINC3              | PINC2       | PINC1             | PINC0        | 88                |

| 0x12 (0x32) | PORTD         | PORTD7         | PORTD6 | PORTD5   | PORTD4            | PORTD3             | PORTD2      | PORTD1            | PORTD0       | 88                |

| 0x11 (0x31) | DDRD          | DDD7           | DDD6   | DDD5     | DDD4              | DDD3               | DDD2        | DDD1              | DDD0         | 88                |

| 0x10 (0x30) | PIND          | PIND7          | PIND6  | PIND5    | PIND4             | PIND3              | PIND2       | PIND1             | PIND0        | 88                |

| 0x0F (0x2F) | SPDR          |                |        |          | SPI Da            | ta Register        |             |                   |              | 169               |

| 0x0E (0x2E) | SPSR          | SPIF           | WCOL   | -        | -                 | -                  | -           | -                 | SPI2X        | 169               |

| 0x0D (0x2D) | SPCR          | SPIE           | SPE    | DORD     | MSTR              | CPOL               | CPHA        | SPR1              | SPR0         | 167               |

| 0x0C (0x2C) | UDR0          |                | 1      | 1        |                   | Data Register      | 1           | 1                 |              | 188               |

| 0x0B (0x2B) | UCSR0A        | RXC0           | TXC0   | UDRE0    | FE0               | DOR0               | UPE0        | U2X0              | MPCM0        | 189               |

| 0x0A (0x2A) | UCSR0B        | RXCIE0         | TXCIE0 | UDRIE0   | RXEN0             | TXEN0              | UCSZ02      | RXB80             | TXB80        | 190               |

| 0x09 (0x29) | UBRR0L        |                |        |          |                   | Rate Register Lo   |             |                   | Г            | 193               |

| 0x08 (0x28) | ACSR          | ACD            | ACBG   | ACO      | ACI               | ACIE               | ACIC        | ACIS1             | ACIS0        | 228               |

| 0x07 (0x27) | ADMUX         | REFS1          | REFS0  | ADLAR    | MUX4              | MUX3               | MUX2        | MUX1              | MUX0         | 243               |

| 0x06 (0x26) | ADCSRA        | ADEN           | ADSC   | ADATE    | ADIF              | ADIE               | ADPS2       | ADPS1             | ADPS0        | 245               |

| 0x05 (0x25) | ADCH          |                |        |          | ADC Data Re       | gister High Byte   |             |                   |              | 246               |

| 0x04 (0x24) | ADCL          |                |        |          | ADC Data Re       | egister Low byte   |             |                   |              | 246               |

| ••••••      |               | DODTE7         | PORTE6 | PORTE5   | PORTE4            | PORTE3             | PORTE2      | PORTE1            | PORTE0       | 88                |

| 0x03 (0x23) | PORTE         | PORTE7         | TORTED | TORTEO   |                   |                    |             |                   |              |                   |

|             | PORTE<br>DDRE | DDE7           | DDE6   | DDE5     | DDE4              | DDE3               | DDE2        | DDE1              | DDE0         | 88                |

## **Register Summary (Continued)**

## **Register Summary (Continued)**

| Address                                                                                                                             | Name | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Page |

|-------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| 0x00 (0x20)                                                                                                                         | PINF | PINF7 | PINF6 | PINF5 | PINF4 | PINF3 | PINF2 | PINF1 | PINF0 | 89   |

| Notes: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses |      |       |       |       |       |       |       |       |       |      |

: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

Some of the status flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on all bits in the I/O Register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

## Instruction Set Summary

| Mnemonics      | Operands        | Description                                                          | Operation                                                                                                  | Flags        | #Clocks    |

|----------------|-----------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------|------------|

| ARITHMETIC AN  | D LOGIC INSTRUC | TIONS                                                                |                                                                                                            |              |            |

| ADD            | Rd, Rr          | Add two Registers                                                    | $Rd \leftarrow Rd + Rr$                                                                                    | Z,C,N,V,H    | 1          |

| ADC            | Rd, Rr          | Add with Carry two Registers                                         | $Rd \leftarrow Rd + Rr + C$                                                                                | Z,C,N,V,H    | 1          |

| ADIW           | Rdl,K           | Add Immediate to Word                                                | $Rdh:Rdl \leftarrow Rdh:Rdl + K$                                                                           | Z,C,N,V,S    | 2          |

| SUB            | Rd, Rr          | Subtract two Registers                                               | $Rd \leftarrow Rd - Rr$                                                                                    | Z,C,N,V,H    | 1          |

| SUBI           | Rd, K           | Subtract Constant from Register                                      | $Rd \leftarrow Rd - K$                                                                                     | Z,C,N,V,H    | 1          |

| SBC            | Rd, Rr          | Subtract with Carry two Registers                                    | $Rd \leftarrow Rd - Rr - C$                                                                                | Z,C,N,V,H    | 1          |

| SBCI           | Rd, K           | Subtract with Carry Constant from Reg.                               | $Rd \leftarrow Rd - K - C$                                                                                 | Z,C,N,V,H    | 1          |

| SBIW           | Rdl,K           | Subtract Immediate from Word                                         | $Rdh:Rdl \leftarrow Rdh:Rdl - K$                                                                           | Z,C,N,V,S    | 2          |

| AND            | Rd, Rr          | Logical AND Registers                                                | $Rd \leftarrow Rd \bullet Rr$                                                                              | Z,N,V        | 1          |

| ANDI           | Rd, K           | Logical AND Register and Constant                                    | $Rd \leftarrow Rd \bullet K$                                                                               | Z,N,V        | 1          |

| OR             | Rd, Rr          | Logical OR Registers                                                 | $Rd \leftarrow Rd \lor Rr$                                                                                 | Z,N,V        | 1          |

| ORI            | Rd, K           | Logical OR Register and Constant                                     | $Rd \leftarrow Rd \lor K$                                                                                  | Z,N,V        | 1          |

| EOR            | Rd, Rr          | Exclusive OR Registers                                               | $Rd \leftarrow Rd \oplus Rr$                                                                               | Z,N,V        | 1          |

| COM            | Rd              | One's Complement                                                     | $Rd \leftarrow 0xFF - Rd$                                                                                  | Z,C,N,V      | 1          |

| NEG            | Rd              | Two's Complement                                                     | Rd ← 0x00 – Rd                                                                                             | Z,C,N,V,H    | 1          |

| SBR            | Rd,K            | Set Bit(s) in Register                                               | $Rd \leftarrow Rd \lor K$                                                                                  | Z,N,V        | 1          |

| CBR            | Rd,K            | Clear Bit(s) in Register                                             | $Rd \leftarrow Rd \bullet (0xFF - K)$                                                                      | Z,N,V        | 1          |

| INC            | Rd              | Increment                                                            | $Rd \leftarrow Rd + 1$                                                                                     | Z,N,V        | 1          |

| DEC            | Rd              | Decrement                                                            | $Rd \leftarrow Rd - 1$                                                                                     | Z,N,V        | 1          |

| TST            | Rd              | Test for Zero or Minus                                               | $Rd \leftarrow Rd \bullet Rd$                                                                              | Z,N,V        | 1          |

| CLR            | Rd              | Clear Register                                                       | $Rd \leftarrow Rd \oplus Rd$                                                                               | Z,N,V        | 1          |

| SER            | Rd              | Set Register                                                         | $Rd \leftarrow 0xFF$                                                                                       | None         | 1          |

| MUL            | Rd, Rr          | Multiply Unsigned                                                    | $R1:R0 \leftarrow Rd \times Rr$                                                                            | Z,C          | 2          |

| MULS           | Rd, Rr          | Multiply Signed                                                      | $R1:R0 \leftarrow Rd \times Rr$                                                                            | Z,C          | 2          |

| MULSU          | Rd, Rr          | Multiply Signed with Unsigned                                        | $R1:R0 \leftarrow Rd \times Rr$                                                                            | Z,C          | 2          |

| FMUL           | Rd, Rr          | Fractional Multiply Unsigned                                         | R1:R0 " (Rd x Rr) << 1                                                                                     | Z,C          | 2          |

| FMULS          | Rd, Rr          | Fractional Multiply Signed                                           | R1:R0 " (Rd x Rr) << 1                                                                                     | Z,C          | 2          |

| FMULSU         | Rd, Rr          | Fractional Multiply Signed with Unsigned                             | R1:R0 " (Rd x Rr) << 1                                                                                     | Z,C          | 2          |

| BRANCH INSTRUC |                 | Haddonar maraphy orginal mar onoighou                                |                                                                                                            | 2,0          | -          |

| RJMP           | k               | Relative Jump                                                        | $PC \leftarrow PC + k + 1$                                                                                 | None         | 2          |

| IJMP           | ĸ               | Indirect Jump to (Z)                                                 | PC ← Z                                                                                                     | None         | 2          |

| JMP            | k               | Direct Jump                                                          | $PC \leftarrow k$                                                                                          | None         | 3          |

| RCALL          | k               | Relative Subroutine Call                                             | $PC \leftarrow PC + k + 1$                                                                                 | None         | 3          |

| ICALL          | ĸ               | Indirect Call to (Z)                                                 | PC ← Z                                                                                                     | None         | 3          |

| CALL           | k               | Direct Subroutine Call                                               | PC ← k                                                                                                     | None         | 4          |

| RET            |                 | Subroutine Return                                                    | PC ← STACK                                                                                                 | None         | 4          |

| RETI           |                 | Interrupt Return                                                     | PC ← STACK                                                                                                 |              | 4          |

| CPSE           | Rd,Rr           | Compare, Skip if Equal                                               | if (Rd = Rr) PC $\leftarrow$ PC + 2 or 3                                                                   | None         | 1/2/3      |

| CP             | Rd,Rr           | Compare                                                              | Rd – Rr                                                                                                    | Z, N,V,C,H   | 1          |

| CPC            | Rd,Rr           | Compare with Carry                                                   | Rd – Rr – C                                                                                                | Z, N,V,C,H   | 1          |

| CPI            | Rd,K            | Compare Register with Immediate                                      | Rd – K                                                                                                     | Z, N,V,C,H   | 1          |

| SBRC           | Rr, b           | Skip if Bit in Register Cleared                                      | if (Rr(b)=0) PC $\leftarrow$ PC + 2 or 3                                                                   | None         | 1/2/3      |

| SBRS           | Rr, b           | Skip if Bit in Register is Set                                       | if $(Rr(b)=1) PC \leftarrow PC + 2 \text{ or } 3$                                                          | None         | 1/2/3      |

| SBIC           | P, b            | Skip if Bit in I/O Register Cleared                                  | if $(P(b)=0) PC \leftarrow PC + 2 \text{ or } 3$                                                           | None         | 1/2/3      |

| SBIS           | P, b            | Skip if Bit in I/O Register is Set                                   | if $(P(b)=1) PC \leftarrow PC + 2 \text{ or } 3$                                                           | None         | 1/2/3      |

| BRBS           | s, k            | Branch if Status Flag Set                                            | if (SREG(s) = 1) then $PC \leftarrow PC+k + 1$                                                             | None         | 1/2        |

| BRBC           | s, k            | Branch if Status Flag Cleared                                        | if (SREG(s) = 0) then $PC \leftarrow PC+k + 1$                                                             | None         | 1/2        |

| BREQ           | k k             | Branch if Equal                                                      | if (Z = 1) then PC $\leftarrow$ PC + k + 1                                                                 | None         | 1/2        |

| BRNE           | k               | Branch if Not Equal                                                  | if (Z = 0) then PC $\leftarrow$ PC + k + 1                                                                 | None         | 1/2        |

| BRCS           | k               | Branch if Carry Set                                                  | if (C = 1) then PC $\leftarrow$ PC + k + 1                                                                 | None         | 1/2        |

| BRCC           | k               | Branch if Carry Cleared                                              | if (C = 0) then PC $\leftarrow$ PC + k + 1                                                                 | None         | 1/2        |

| BRSH           | k               | Branch if Same or Higher                                             | if (C = 0) then PC $\leftarrow$ PC + k + 1                                                                 | None         | 1/2        |

| BRLO           | k               | Branch if Lower                                                      | if (C = 1) then PC $\leftarrow$ PC + k + 1                                                                 | None         | 1/2        |

| BRMI           | k               | Branch if Minus                                                      | if (N = 1) then PC $\leftarrow$ PC + k + 1                                                                 | None         | 1/2        |

| BRPL           | k               | Branch if Plus                                                       | if (N = 0) then PC $\leftarrow$ PC + k + 1                                                                 | None         | 1/2        |

| BRGE           | k k             | Branch if Greater or Equal, Signed                                   |                                                                                                            |              | 1/2        |

|                |                 |                                                                      | if $(N \oplus V=0)$ then PC $\leftarrow$ PC + k + 1<br>if $(N \oplus V=1)$ then PC $\leftarrow$ PC + k + 1 | None         |            |

| BRLT           | k               | Branch if Less Than Zero, Signed                                     | if $(N \oplus V = 1)$ then PC $\leftarrow$ PC + k + 1<br>if $(H = 1)$ then PC $\leftarrow$ PC + k + 1      | None         | 1/2        |

| BRHS           | k               | Branch if Half Carry Flag Set                                        | if (H = 1) then PC $\leftarrow$ PC + k + 1<br>if (H = 0) then PC $\leftarrow$ PC + k + 1                   | None         | 1/2        |

| BRHC           | k               | Branch if Half Carry Flag Cleared                                    | if $(H = 0)$ then $PC \leftarrow PC + k + 1$                                                               | None         | 1/2        |

| BRTS           | k               | Branch if T Flag Set                                                 | if (T = 1) then PC $\leftarrow$ PC + k + 1<br>if (T = 0) then PC $\leftarrow$ PC + k + 1                   | None         | 1/2        |

| BRTC           | k               | Branch if T Flag Cleared                                             | if (T = 0) then PC $\leftarrow$ PC + k + 1                                                                 | None<br>None | 1/2<br>1/2 |

|                |                 |                                                                      |                                                                                                            | NODA         | 1/2        |

| BRVS<br>BRVC   | k<br>k          | Branch if Overflow Flag is Set<br>Branch if Overflow Flag is Cleared | if (V = 1) then PC $\leftarrow$ PC + k + 1<br>if (V = 0) then PC $\leftarrow$ PC + k + 1                   | None         | 1/2        |

## Instruction Set Summary (Continued)

| Book         Internet Product Product         Internet Product         Internet Product         Internet Product         Internet Product           MAY         Bask Product Product         Main Product Product         Main Product Product         Main Product Product         Main Product Product Product         Main Product Product Product         Main Product Produc                                                                                                                                 | 2015                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 111 DO DO 11 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                 |                       |                             |                                                   |                                             |              |     |